Introduction

The FPGA Clarinet Simulator is an application developed in C that simulates the notes produced by a B♭ clarinet. FPGA Clarinet Simulator runs natively on Terasic’s DE1-SoC FPGA and is compiled using Quartus.

Key Features

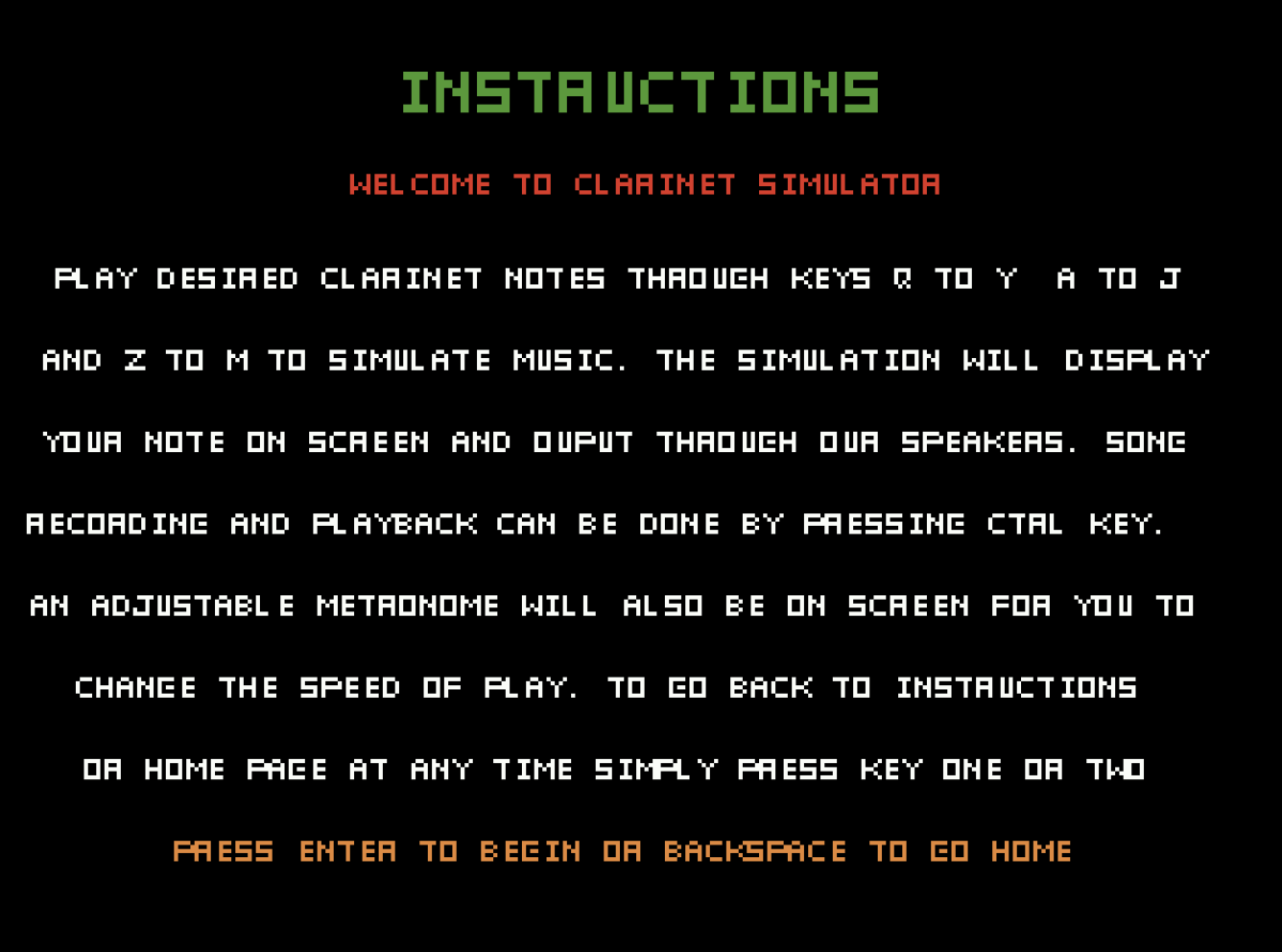

Instructions Screen

The instructions screen contains all possible ways the user can interact with the simulator. The characters are transcribed into a collection of pixel in order to be displayed on the VGA display.

Figure 1. Instructions screen.

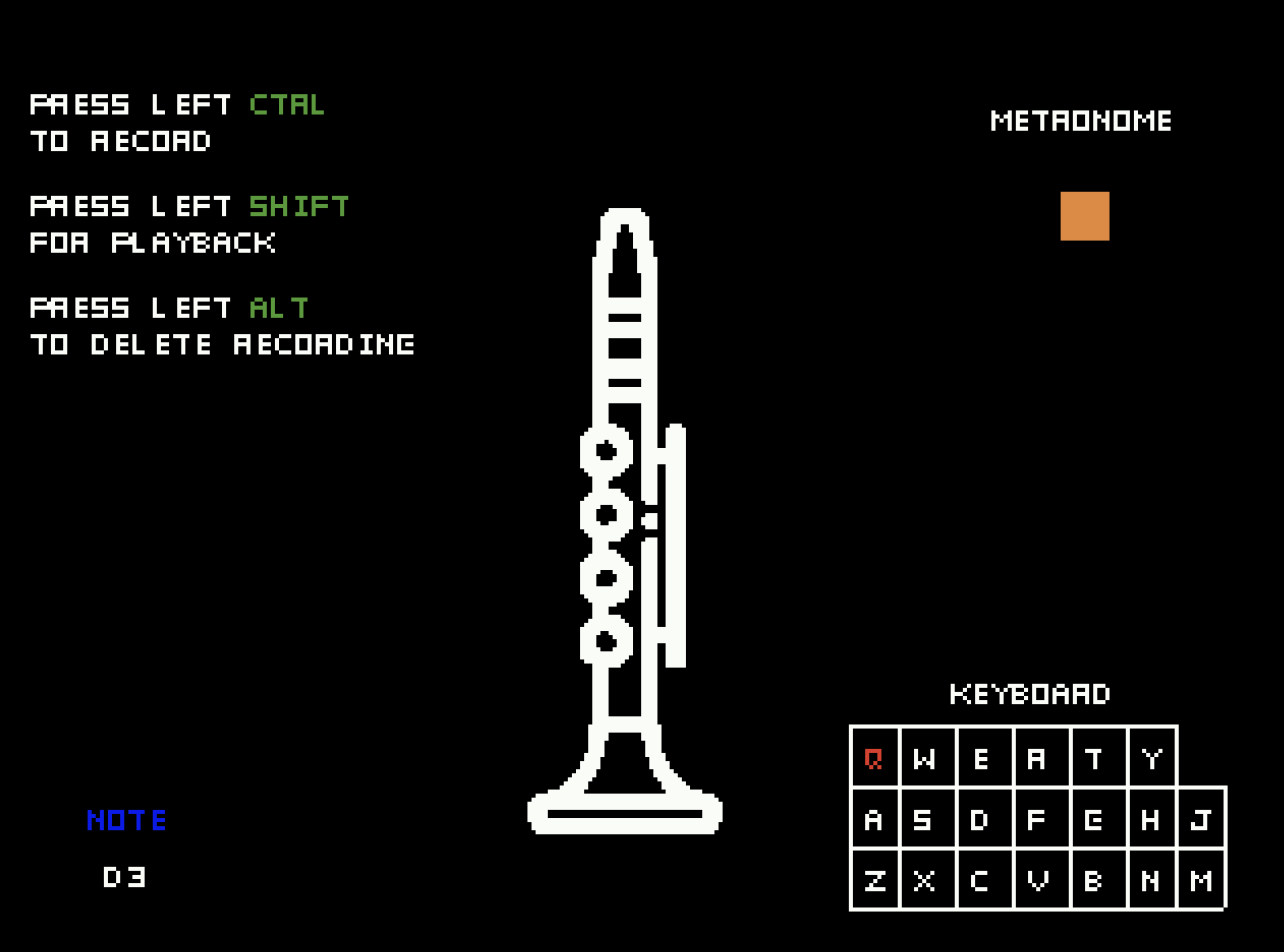

Keyboard Input

The main interactions (playing notes, recording operations, etc.) with the simulator are accomplished through the PS/2 keyboard. With consistent polling implemented, the simulator is responsive to each key press or hold. The key presses and holds are dynamically indicated on the VGA screen.

Figure 2. Key press visualization.

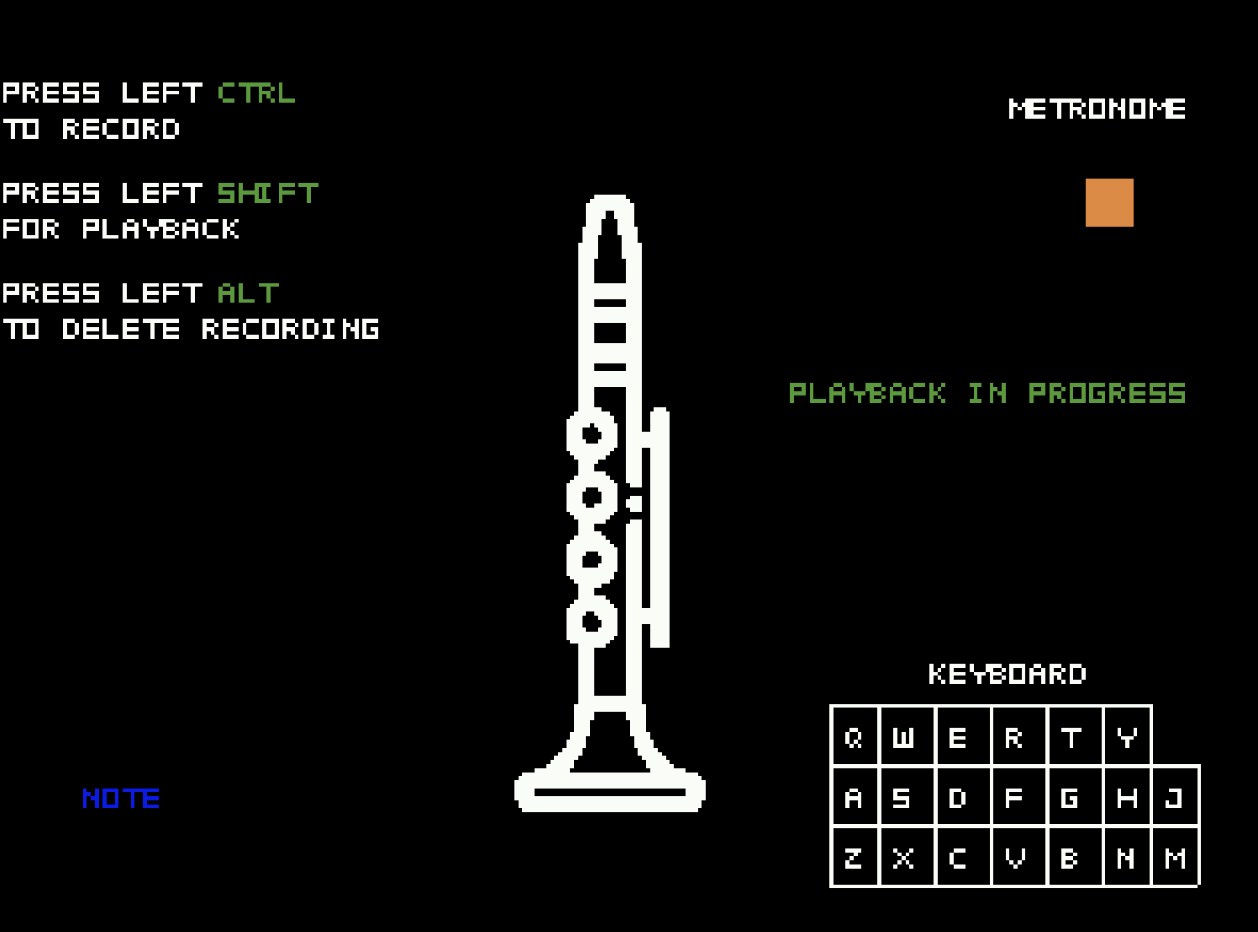

Recording & Playback

The simulator is capable of “recording” the notes played by storing the audio snippets into on-board memory, for playback or deletion later on. To assist with more challenging music pieces, an animated metronome is built-in. The user is informed of each process ongoing through the dynamically-rendered GUI displayed on the VGA screen.

Figure 3. Playback and metronome in action.

Wrapping Up

There are more technical details than what have been introduced above. The FPGA Clarinet Simulator is a challenging project that built my skills in FPGA programming and UI design.

Source Code

Due to university policy, the source code of the FPGA Clarinet Simulator generally needs to remain private. However, if source code is required for purposes such as employment screening, please contact me.